# AMDA

# AMD 400G Adaptive SmartNIC SoC

**Technology preview**

Jaideep Dastidar

Co-authors: David Riddoch, Jason Moore, Steve Pope, Jim Wesselkamper

Hot Chips 2022

# Agenda

| Overview                                        | <ul> <li>Motivating factors behind SmartNICs</li> <li>AMD 400G Adaptive SmartNIC SoC Objectives</li> </ul>                                                                       |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Solution –<br>AMD 400G Adaptive<br>SmartNIC SoC | <ul> <li>Offload Acceleration Blocks for Host, Network, and Embedded Processing</li> <li>Adaptive Extensions</li> <li>Pervasive Security and Confidential Computing</li> </ul>   |

| Use Case Examples                               | <ul> <li>OVS Offload</li> <li>VirtIO Net Offload</li> <li>Host-Attached Adaptive Network Offload Accelerator</li> <li>Network Attached Adaptive NVMe Storage Endpoint</li> </ul> |

| Summary                                         |                                                                                                                                                                                  |

| Q&A                                             |                                                                                                                                                                                  |

## Overview

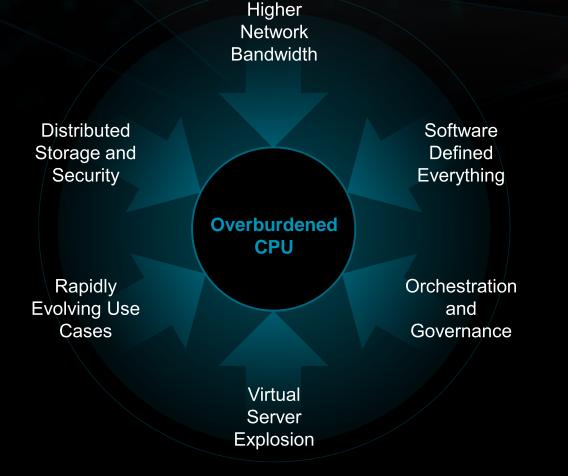

## Motivations for Adaptable, Intelligent Infrastructure

#### Intelligent Infrastructure for Next Gen Applications

**Next Generation Bandwidth** 400Gb Data Processing

Infrastructure Acceleration Maximize CPU revenue potential

High Security Multi-tenant Isolation and Protection

New Trends Expose Current Infrastructure Challenges

## **SmartNIC Solution Space**

## We are at an Architectural Inflection Point

Performanci

FICXIBILIT

## **Tug-of-War between**

## **ASIC-like Fixed Function Logic**

Frequent vs occasional functions

#### **Embedded Processor Cores**

Workload flexibility vs processing offload

### **FPGAs or Programmable Logic**

Adapting new and existing functions

Security

## AMD 400G Adaptive SmartNIC SoC Objectives

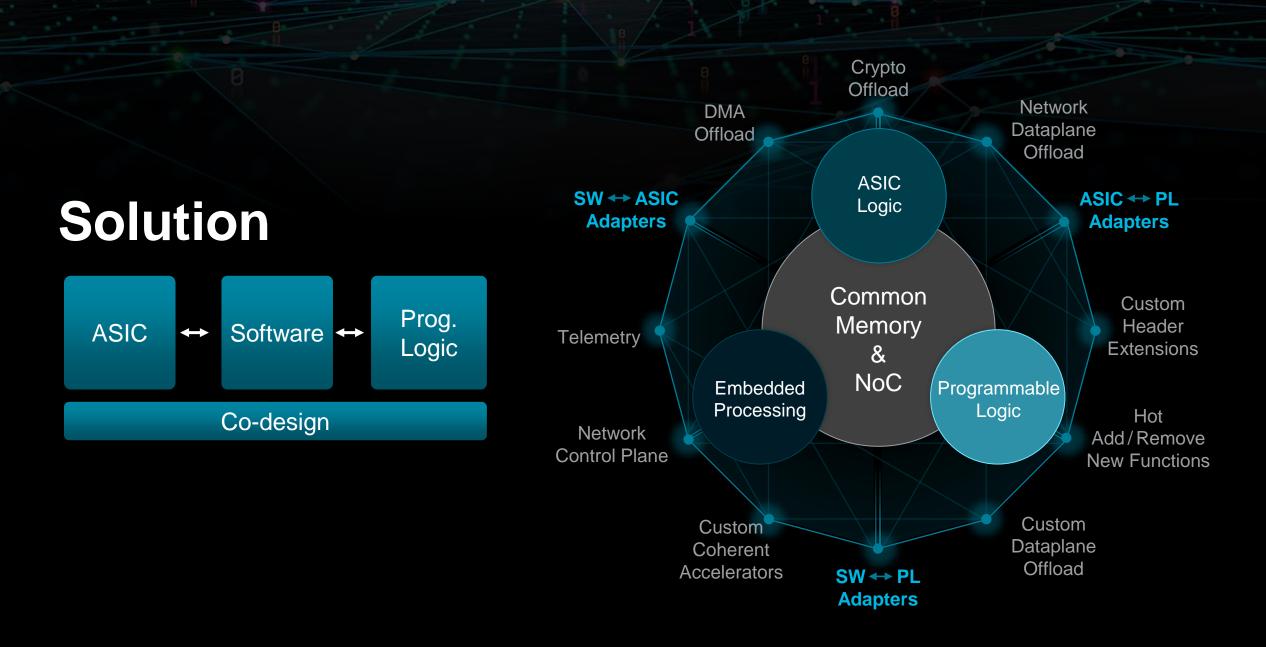

#### **Balanced Architecture**

- Architect an adaptive SoC for the SmartNIC domain

- Strike the right balance between the heterogeneous elements

- Present a unified software view of the heterogeneous element SoC

#### **Performance and Adaptability**

- Latest Interfaces/Speeds: 112G Ethernet, PCIe Gen5, CXL 2.0, LPDDR5/DDR5

- Adaptive Interface APIs for evolving workloads and customization

#### Security

- Latest security standards: PCIe, OCP and NIST

- Symmetric and asymmetric crypto offload for data encryption and key exchange

- Physical and logical isolation for confidential compute

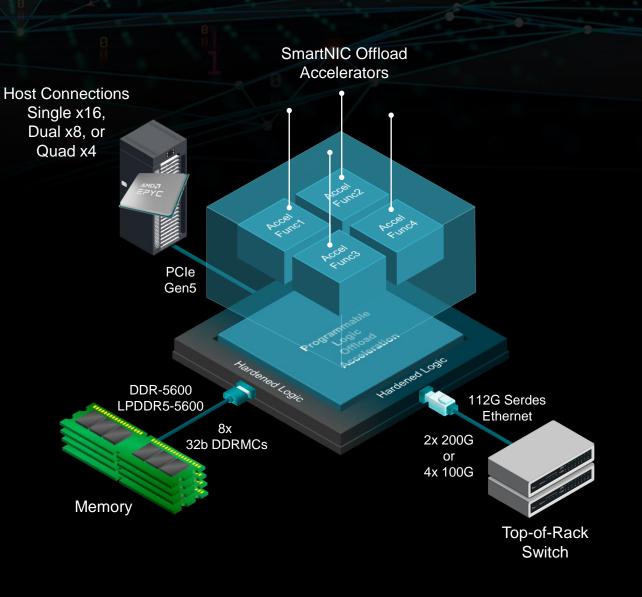

## AMD 400G Adaptive SmartNIC SoC

Technology preview

## **Tightly Coupled SmartNIC Blocks**

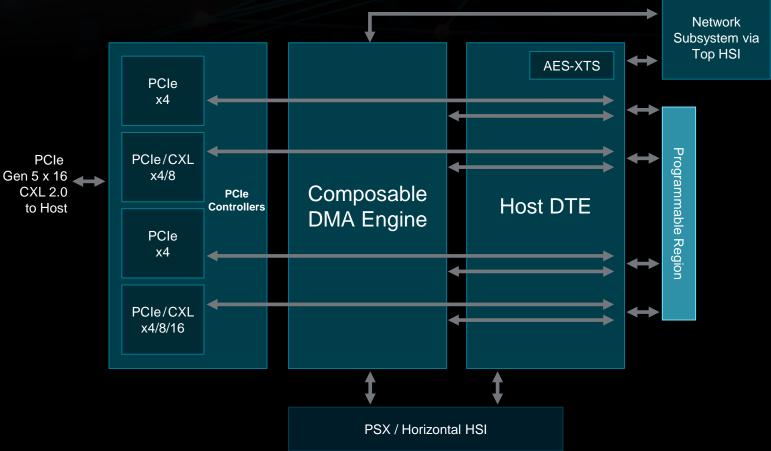

**CPM5N: Host Subsystem Overview**

# PCIe Gen 5 or CXL 2.0 host connection

Composable DMA (CDx)

Host DTE (Data Transform Engine)

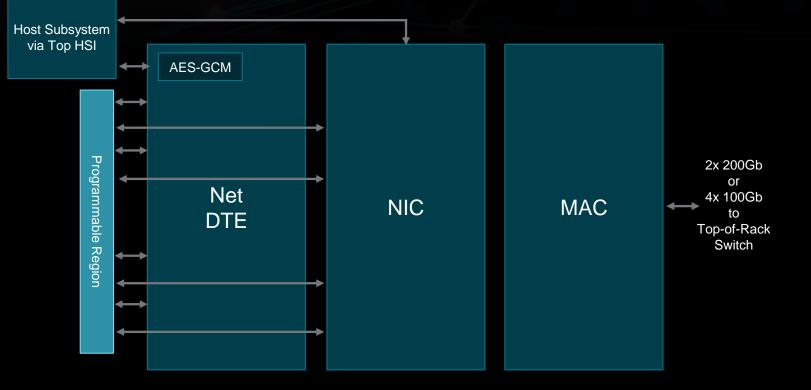

## **HNICX: Networking Subsystem Overview**

## Network DTE (Data Transform Engine)

MAC

## **Memory Subsystem Overview**

### **8x LPDDR5 / DDR5 Controllers**

- 32-bit DDR5-5600 with ECC or

- 16-bit, 32-bit, or dual 160-bit LPDDR-6400 with ECC

- Inline Memory Encryption

AES-GCM / AES-XTS with DPA countermeasures

### **DDR Controller Bypass Mode for SCM**

- PHY also supports other standards such as MIPI

- Custom PL Controllers for Storage Class Memory

Inline Memory Encryption

8x 32b LPDDR5/DDR5 Controllers

LPDDR5/DDR5 PHY

# **Processing Subsystem (PSX) Overview**

CPM5N PL HNICX PSX LP/DDR

|                                       | LPD                                   |                                              |                                          | FPD    |                                                   |                                                   |     |                                           |                                    |

|---------------------------------------|---------------------------------------|----------------------------------------------|------------------------------------------|--------|---------------------------------------------------|---------------------------------------------------|-----|-------------------------------------------|------------------------------------|

| 4 real-time cores arranged as Two     | Cortex-R52<br>32KB I/D\$<br>128KB TCM | <b>Cortex-R52</b><br>32KB I/D\$<br>128KB TCM | <b>Cortex-A7</b><br>64KB I\$/<br>512KB L | /D\$   | <b>Cortex-A78AE</b><br>64KB I\$/D\$<br>512KB L2\$ | <b>Cortex-A78AE</b><br>64KB I\$/D\$<br>512KB L2\$ | 64ł | <b>ex-A78AE</b><br>(B I\$/D\$<br>2KB L2\$ | High Pe<br>Domain                  |

| 2-core Clusters w/<br>Tightly-Coupled | LS/Split                              | LS/Split                                     | LS/Spli                                  | it     | LS/Split                                          | LS/Split                                          | L   | S/Split                                   | 16 Applic                          |

| Memory                                | Cortex-R52<br>32KB I/D\$<br>128KB TCM | <b>Cortex-R52</b><br>32KB I/D\$<br>128KB TCM | <b>Cortex-A7</b><br>64KB I\$/<br>512KB L | /D\$   | Cortex-A78AE<br>64KB I\$/D\$<br>512KB L2\$        | Cortex-A78AE<br>64KB I\$/D\$<br>512KB L2\$        | 64ł | <b>ex-A78AE</b><br>(B I\$/D\$<br>2KB L2\$ | arranged<br>4-core Clu<br>w/Crypto |

|                                       | Interconnect                          |                                              | L3 Cach<br>2MB                           |        | L3 Cache<br>2MB                                   | L3 Cache<br>2MB                                   |     | Cache<br>2MB                              |                                    |

|                                       | 1MB OCM                               | DMA                                          |                                          |        |                                                   |                                                   |     |                                           |                                    |

|                                       | GbE (2)                               | CANFD (2)                                    | Coherency Mesh Network                   |        |                                                   |                                                   |     |                                           |                                    |

|                                       | USB2 (2)                              | UART (2)                                     | LLC<br>16MB                              |        |                                                   |                                                   |     |                                           |                                    |

|                                       | SPI (2)                               | I2C+I3C (2)                                  |                                          |        |                                                   |                                                   |     |                                           |                                    |

|                                       | MIO                                   | Timers                                       | Core                                     | System | n Interc                                          | onnect                                            | GIC | PKI                                       | Public Key<br>TLS 1.3              |

|                                       | PSM<br>PS Mgmt                        | Debug<br>PS CoreSight                        | Sight                                    | MMU    |                                                   |                                                   |     |                                           | Offload Ac                         |

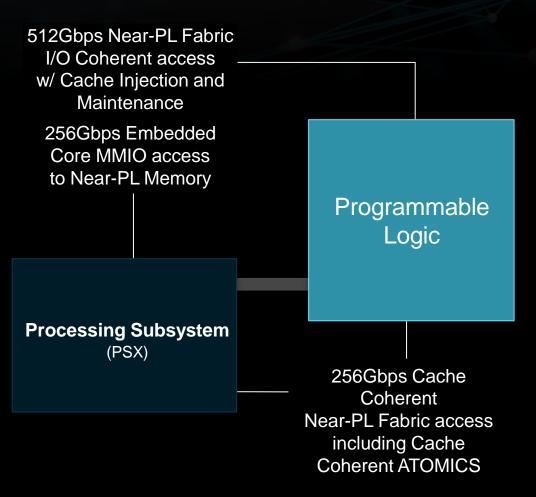

# Tight Coupling between CPM5N + PSX

256Gbps Host MMIO to Embedded Cores Data Flow w/ Cache Injection via PCIe/CXL.io Endpoint 256Gbps

Embedded Cores to Host Data/Doorbells Processing Subsystem (PSX)

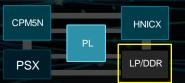

# Tight Coupling between Prog. Logic ↔ PSX

##

## Security and Confidential Compute Across Domain-specific Accelerators

mirror object to mirror rror\_mod.mirror\_object eration == "MIRROR\_X": rror\_mod.use\_x = True rror\_mod.use\_y = False rror\_mod\_use\_z = False operation == "MIRROR y" rror\_mod.use\_x = failse rror\_mod.use\_y = Inte rror\_mod.use\_z = False **Operation** == "MIRROR Z" **rror\_mod\_use\_x** = False rror\_mod.use\_y = False **Pror\_mod.use\_z** = True ob.select= ntext.scene.objects.actim "Selected" + str(modifier bpy.context.selected\_obj ata.objects[one.name].sel int("please select exactle i - OPERATOR CLASSES (ypes.Operator):

x mirror to the selected x mirror to the selected ject.mirror\_mirror\_x" ror X"

ontext): oxt.active\_object is not

## **Pervasive Security**

Layers of Security

CHECK

Secure Boot, Key Exchange and Attestation AMD keys, SmartNIC owner keys, and SmartNIC tenant keys

## PROTECT

Memory and Peripheral Protection Units SoC-wide hardware firewalls for tenants and accelerators

## SHIELD

#### Secure Data in Flight, at Rest, in Use

Encryption for data, host/network interfaces, and DRAM Secure monitors for external, internal, physical attacks Crypto engines with DPA countermeasure protection

## **Use Case Examples**

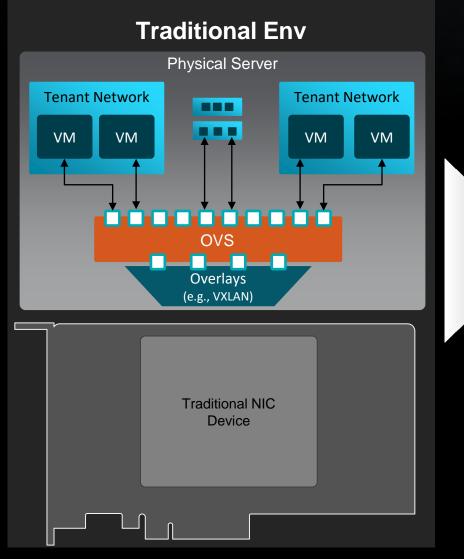

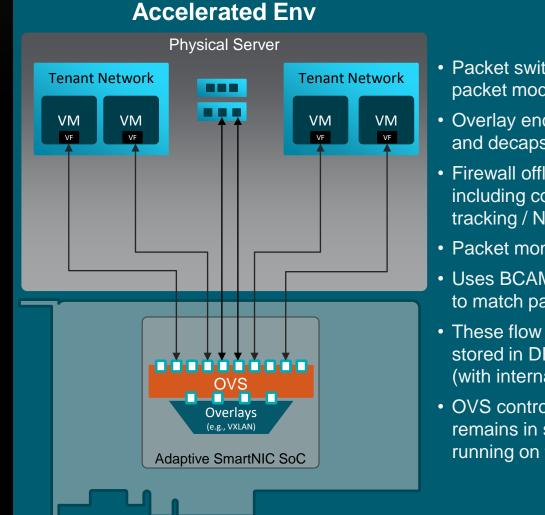

## **Full OVS Offload**

- Packet switching and packet modifications

- Overlay encapsulation and decapsulation

- Firewall offload including connection tracking / NAT

- Packet monitoring

- Uses BCAM / TCAM to match packet flows

- These flow tables stored in DRAM (with internal caching)

- OVS control plane remains in software running on the host

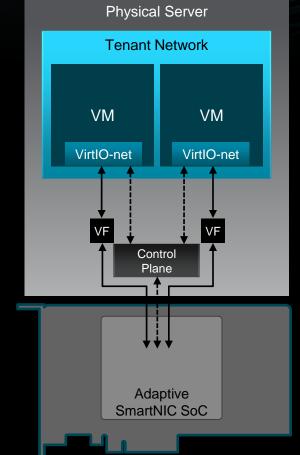

## **VirtlO-net Support**

## Device Natively Supports VirtIO Queues

#### **Two Deployment Models**

- Bare Metal VirtIO

- vDPA

- (Virtual Data Path Acceleration)

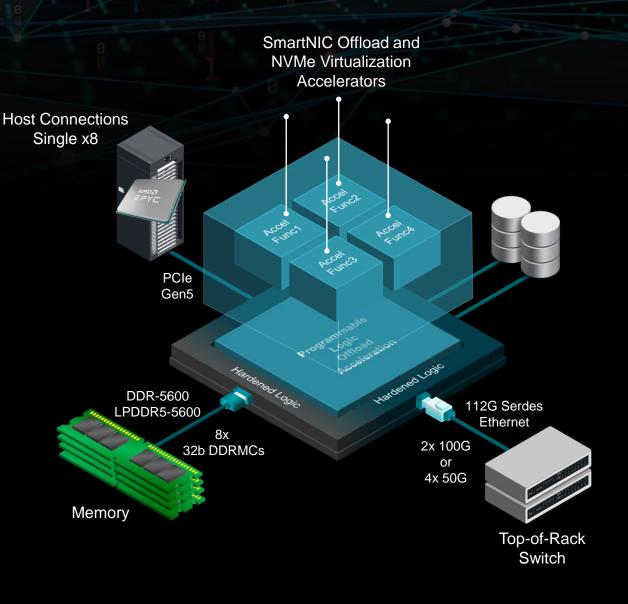

## PCIe Endpoint 400G SmartNIC w/ with Host Storage and Network Offload

- Standard Ethernet Packet Flow

- Custom Header, Encapsulation, or Encryption Flow

- Host Connection with Advanced Switch Hot Plug

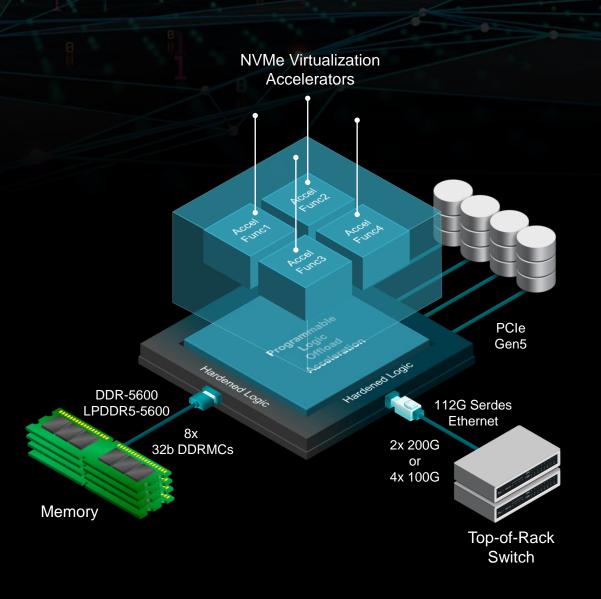

## PCIe Endpoint 200G SmartNIC w/ 2 Gen5 x4 NVMe SSDs

- Host endpoint connection NVMe virtualization

- SmartNIC Root-Port connections for dual-NVMe SSDs w/ AES-XTS offload acceleration

- 2x 100G or 4x 50G network connection

## PCIe Root Complex 400G NVMe Storage Node

- Network-attached storage appliance

- SmartNIC Root-Port connections for quad-NVMe SSDs

w/ AES-XTS offload acceleration

- 2x 200G or 4x 100G remote storage connections

# Summary

## **Performance & Resources**

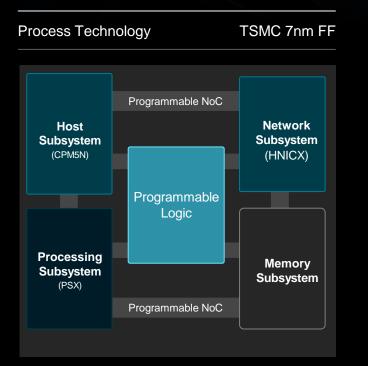

#### Manufacturing Technology

#### **Architectural Resources**

| Host subsystem                      | PCIe Gen5 x16<br>PCIe CMA/DOE/IDE<br>CXL v2.0                         |

|-------------------------------------|-----------------------------------------------------------------------|

| Network subsystem                   | 2x 200G Ethernet<br>Virtual switch offload<br>Stateless offloads      |

| Application Processing<br>Subsystem | 16x A78-AE<br>24MB Shared Cache                                       |

| Real-time Processing Subsystem      | 4x ARM R52                                                            |

| PKI (TLS1.3 Offload Engine)         | Yes                                                                   |

| DDR subsystem                       | 8x 32b LPDDR5/DDR5<br>ECC<br>Inline encryption<br>1.638Tb/s LPDDR5 BW |

#### SmartNIC SoC Performance<sup>†</sup>

| Programmable logic packet rate <sup>1</sup> | 400Mpps Ingress<br>+ 400Mpps Egress |

|---------------------------------------------|-------------------------------------|

| Host ⇔ Network packet rate <sup>2</sup>     | 400Mpps RX<br>+ 400Mpps TX          |

| Full Virtio.NET offload BW <sup>3</sup>     | 400Gbps RX<br>+ 400Gbps TX          |

| AES-XTS offload BW <sup>4</sup>             | 800Gb/s                             |

| AES-GCM offload BW <sup>5</sup>             | 800Gb/s                             |

# Thank You

To the worldwide AMD AECG team and all the other AMD teams who made the AMD 400G Adaptive SmartNIC possible

Their creativity, ingenuity, and unwavering dedication to the project has made for a unique Adaptive SmartNIC DSA

## Endnotes

+ SmartNIC SoC performance claims are based on simulation results of pre-silicon models with AMD traffic generators used to emulate external port traffic behavior as of August 23, 2022. Actual performance of production silicon may vary.

1. Interface packet rate between Programmable logic and the Network subsystem

- 2. Sustained TX and RX packet rate for 64B packets

- 3. Sustained TX and RX BW with 1500B payload per packet

- 4. Sustained BW for 1KB packets; Encrypt-only, Decrypt-only, or 400Gb/s Encrypt + 400Gb/s Decrypt with Network Interface configured to 2x200G Ethernet ports

- 5. Sustained BW for 1KB packets; 400Gb/s Encrypt + 400Gb/s Decrypt with Network Interface configured to 2x200G Ethernet ports

- 6. #4 and #5 were also measured concurrently enabled

## **Disclaimer and Attribution**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **ATTRIBUTION**

© 2022 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, the Xilinx logo, Versal, and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions.

# AMD together we advance\_

Thank You for Participating