## August 21, 2022

## CXL3 Fabric – Introduction and use cases

Tony Brewer, Micron & Nathan Kalyanasundharam, AMD

Copyright | CXL<sup>™</sup> Consortium 2022 - Hot Chips 2022 - CXL Tutorial

- Motivation & Use Cases

- Why CXL 3.0 Fabric

- Fabric Basics and Scope

- Port Based Routing

- GFAM Device Transaction Flows

- Host Address Map

- Address Interleaving

- Device Media Partitions

- GFAM Device Media Access Protection

- Summary

# CXL3 Fabric – Motivation

- Explosive data growth

- Data stored and analyzed continuously

- Data volume and velocity demand large clusters for timely analysis

- Significant power to move and copy data

- There is a need for an efficient low latency and high bandwidth solution which minimizes data movement

Explosive growth of data and applications

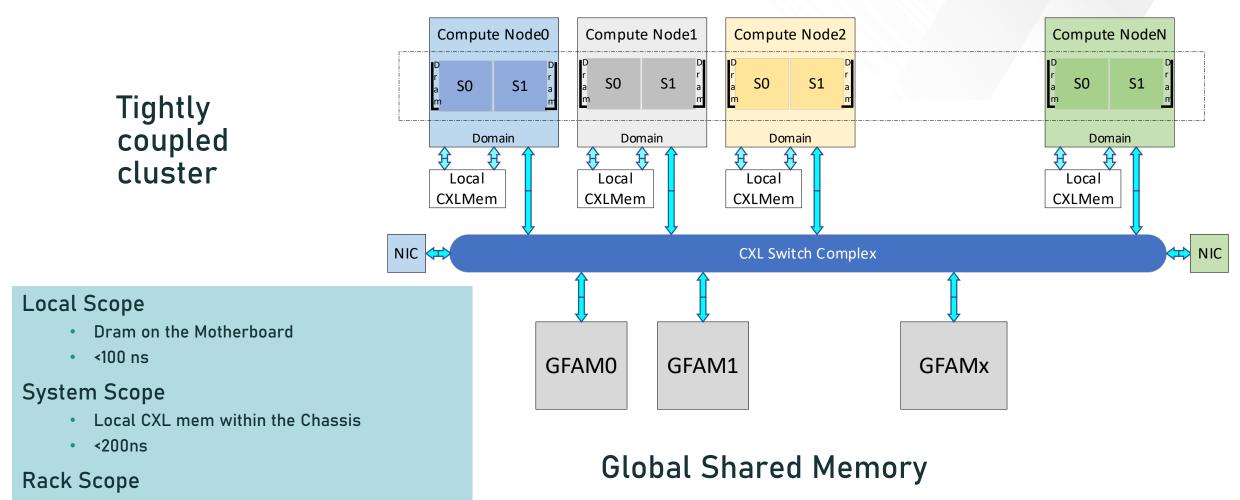

# CXL3 Fabric – Use Case Topology

- Disaggregated global memory within the Rack

- <600 ns

8/21/2022

# CXL3 Fabric – Memory Centric Computing

• HPC/AI/HPDA workloads consume significant amount of power

- Optimize compute to happen near the data

- Enable near and in-memory compute

Copyright | CXL<sup>™</sup> Consortium 2022 - Hot Chips 2022 - CXL Tutorial

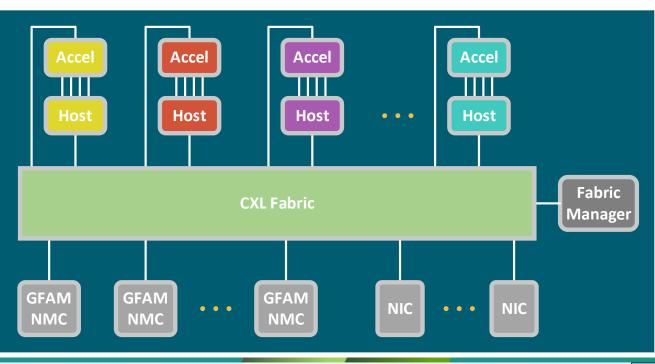

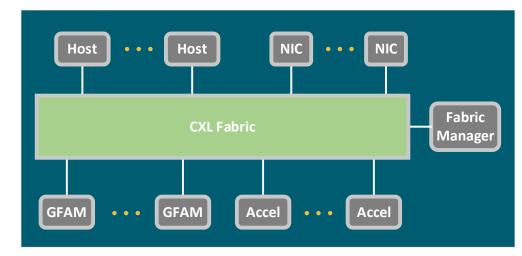

# Why CXL3 Fabric

- CXL 2.0 mechanisms scale to 16 hosts (MLD) per CXL memory device targeting pooling and limited sharing

- CXL 3.0 fabric addresses the large, scalable system space. 100's of hosts, 1000's of memory devices

- CXL 3.0 extends capabilities and introduces scalable mechanisms to support rack and pod scale systems

- Expanded switching topologies

- Enhanced coherency capabilities

- Globally shared fabric attached memory

- Peer-to-peer resource sharing

- CXL 3.0 defines the foundation for CXL fabric-based systems, future ECNs and specification releases are planned to standardize additional aspects

#### CXL3 Fabric based system

6

Copyright | CXL<sup>™</sup> Consortium 2022 - Hot Chips 2022 - CXL Tutorial

## CXL3 Fabric – Basics and Scope

- Port Identifiers

- Source Port (SPID)

- Destination Port (DPID)

- 4096 edge ports (12-bits)

- Each edge port assigned a unique port identifier

- G-FAM devices (GFD)

- Scalable memory resource

- Accessible by all host and devices in the cluster

Load/store memory semantics

**CXL** Switch **CXL** Switch **CXL** Switch Spine **CXL** Switch **CXL** Switch CXL Switch Leaf Edge Ports Fabric CPU CPU Accelerator 1/0 GFAM GFAM I/O Memory GFAM Accelerator Memory GFAM Manager

Nodes

#### 8/21/2022

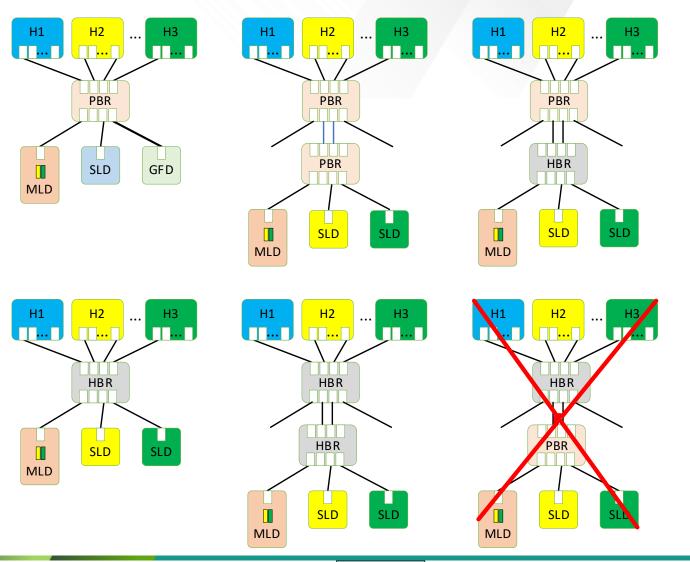

# CXL3 Fabric - Port Based Routing

Copyright | CXL<sup>™</sup> Consortium 2022 - Hot Chips 2022 - CXL Tutorial

- CXL 3.0 augments the previously defined Hierarchy Based Routing with Port Based Routing

- Limited compatibility is defined for fabrics with a combination of Hierarchy and Port Based Routing capable CXL switches

### Acronyms

- HBR = Hierarchy Based Routing

- PBR = Port Based Routing

- SLD = Single logical device

- MLD = Multi logical device

- GFD = Global Fabric Attached Memory Device

Compute \ Express

#### Copyright | CXL<sup>™</sup> Consortium 2022 - Hot Chips 2022 - CXL Tutorial

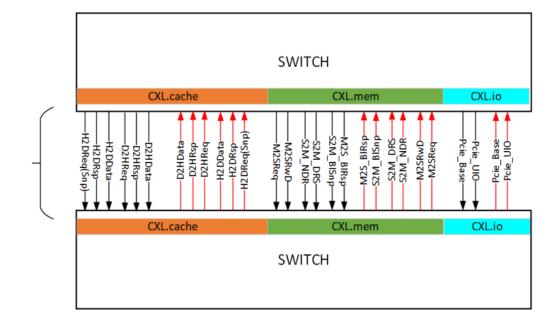

## CXL3 Fabric - Inter-Switch Links

- Previous revisions of CXL required an upstream port and a separate down stream port

- An Inter-Switch Link has been defined for CXL 3.0 allowing a single CXL switch port to act as both an upstream and downstream port

- Allows fewer ports used for interswitch connections and better bandwidth utilization across switch ports

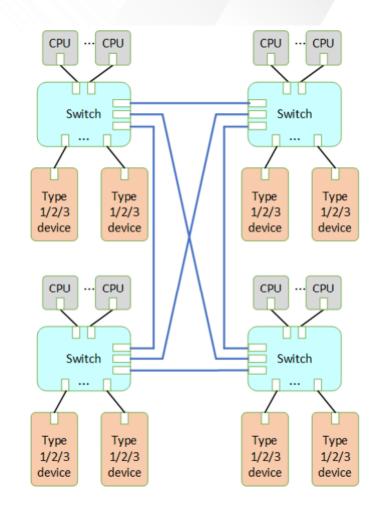

## CXL3 Fabric – Example PBR Mesh Topology CXL Compute Express

- Diagram shows a simple mesh topology with all CPU-to-device accesses being 1 or 2 switch hops

- Limiting the switching hops to at most two will help minimizing FAM access latency

- Eight CPUs are shown in the diagram, but with high radius CXL switches, much larger configurations are possible and still achieve at most two switch hops

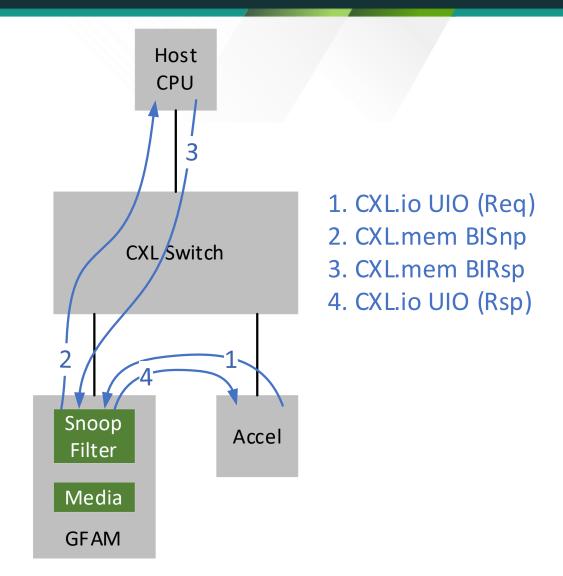

# CXL3 Fabric – GFDTransaction Row

- GFD is accessed using CXL.mem or CXL.io UIO

- Master to Subordinate Request

- Switch Ingress Edge Port

- Decodes address to identify target

- Adds 12-bit SPID and DPID

- Generate PBR Flit

- Switch Egress Edge Port

- Forward PBR Flit to the device

- Device Ingress

- Normalize address and access protection checks

- Subordinate to Master Response

- Device Egress

- Format response packet (native PBR)

- Use request SPID as response DPID

- Switch Egress Edge Port

- Drop DPID and return response to the host

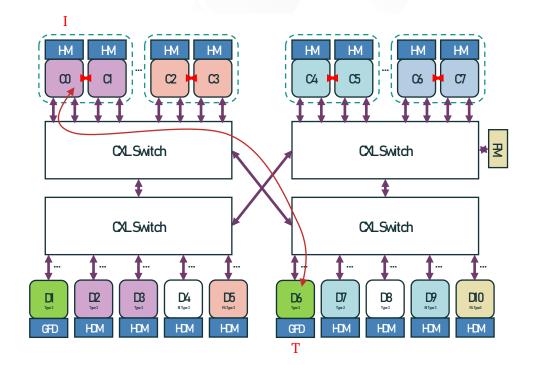

# CXL3 Fabric - CXLmem Back Invalidate

- CXL 2.0 supported Host / Accelerator data sharing with limited additional functionality

- CXL 3.0 Back Invalidate enables inclusive snoop filters and peerto-peer memory requests

Compute

Express

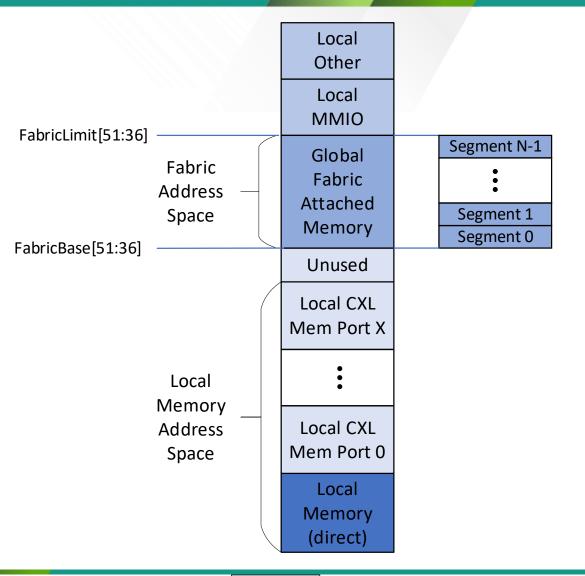

# CXL3 Fabric - Host Physical Address Map

- Each host system has private local memory

- Dram attached to local sockets and

- Memory expansion over CXL

- Memory typically owned by OS or Hypervisor running on the system

- New Fabric address space within the host physical address (HPA) space

- Contiguous address range

- Each host may map a subset or the entire global shared memory space

- Address space typically owned by a central resource manager

- Fabric address space divided in to 'N' segments

- Host is not required to be aware of segments

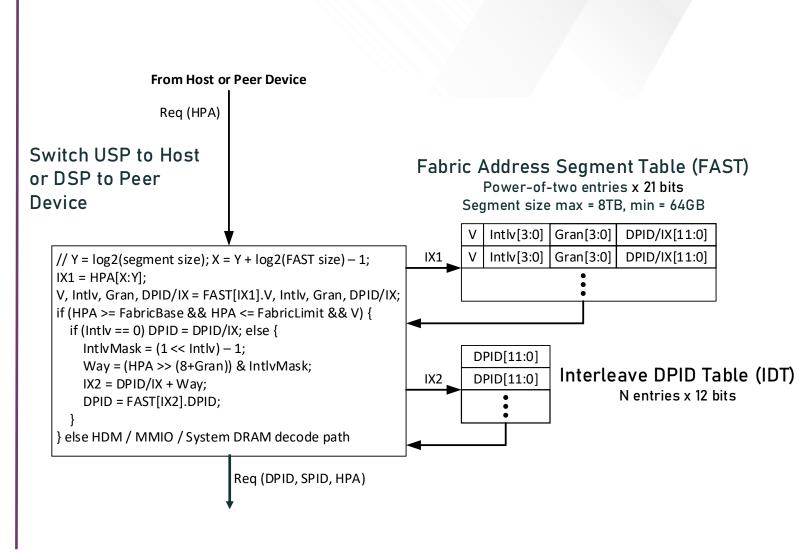

# CXL3 Fabric - Request Address Decode

- Source ID (SPID) identifies the requestor

- Destination ID(DPID) identifies the end point of request

- SPID and DPID added to request by switch ingress port

- Switch uses DPID to route requests and responses to their destination

- Fast Address Segment Table (FAST) and Interleave DPID Table (IDT) are setup by secure firmware running on host or a fabric manager

Compute Express

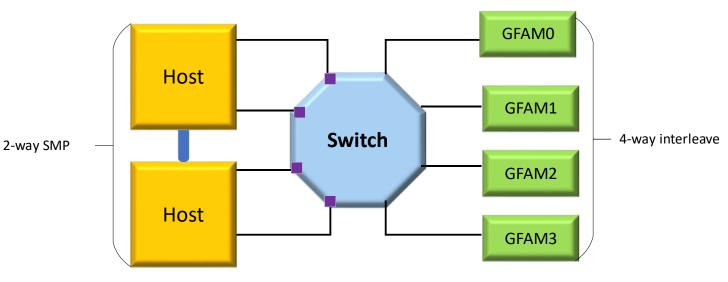

## CXL3 Fabric – Simple Address Interleave

- Host may interleave on any interleave granularity

- Switch edge port will decode and interleave requests to the target GFD port

- Device decodes and normalizes from HPA -> DPA

- Device maintains knowledge of the number of GFDs in the interleaved set

Compute

Express ∖Link™

# CXL3 Fabric – Switch Plane Interleaving

Host

Host

Host

Host

4-way interleave @4KB boundary

Addr[13:12]

- Four independent switch planes

- Host interleaves traffic across four host links

- Each switch further interleaves across four devices

- Device maintains knowledge of interleaved set of 16

- Host interleave in this configuration must use bits within the GFD interleave granularity

GFAM15

GFAM11

GFAM7

GFAM3

GFAM14

GFAM10

GFAM6

GFAM2

GFAM13

GFAM9

GFAM5

GFAM1

GFAM12

GFAM8

GFAM4

Switch

16-way interleave – @4KB boundary Addr[15:14]

Compute E×press Link ™

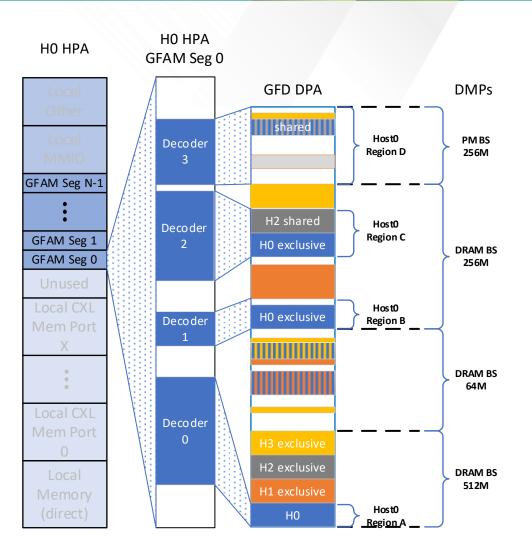

# CXL3 Fabric - GFD Media Partitions

- G-FAM device (GFD) may support multiple device media partitions (DMPs)

- Fundamental attribute of DMP is the media type

- G-FAM device has up to eight decoders per host (SPID). The decoders map portions of HPA to device media partitions.

- CXL 3 supports unique per host physical address ranges to be mapped to each G-FAM device. However, the device physical address is common for all hosts.

# CXL3 Fabric - Device PA Generation

• SPID is used to access the GFD decoder table

- GFD Decoder Table (GDT) 4K entry RAM; for 1TB device N\_Regions \* 58 bits wide

- DPALen0 Coh0 HPABase0 DPABase0 Way0 Gran0 Intlv0 lvo Opt 1 to 7 Request HPA compared against all SPID[11:0] [51:36] [Y:28] [Y:28] [3:0] [3:0] [7:0] DPALen0 Way0 decoders associated with the HPABase0 DPABase0 Intlv0 Gran0 VO Coh0 Opt 1 to 7 [Y:28] [3:0] [51:36] [Y:28] [3:0] [7:0] requester . • DPABaseN added to the offset to derive final DPA parallel for (N=0; N<N Regions; N++) { Offset = Remove Intly Bits (HPA – HPABaseN, IntlyN, GranN); if (Offset >= 0 && Offset < DPALenN\*256MB && VN) { DPA = DPABaseN + Offset; Zero or multi-range hit results in access error DPA

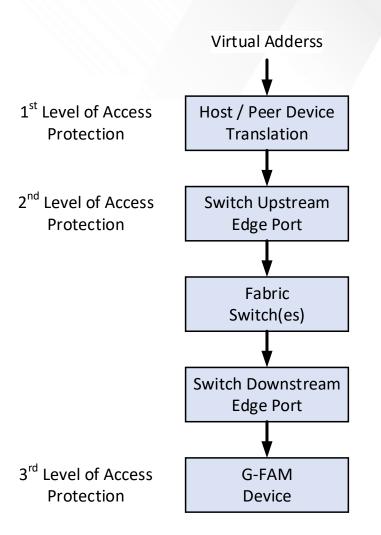

## CXL3 Fabric – GFD Media Access Protection CXL Compute Express Link

#### Requestor's translation provides:

- 1<sup>st</sup> level of access protection and process separation

- VA  $\rightarrow$  Guest PA  $\rightarrow$  Host PA

### Switch request ingress port provides:

- 2<sup>nd</sup> level of access protection

- FAST and IDT must be programmed to access the target GFD

- G-FAM device provides:

- 3<sup>rd</sup> level of access protection

- Device implements Source ID (SPID) based structures to enable access to DC Regions within device media

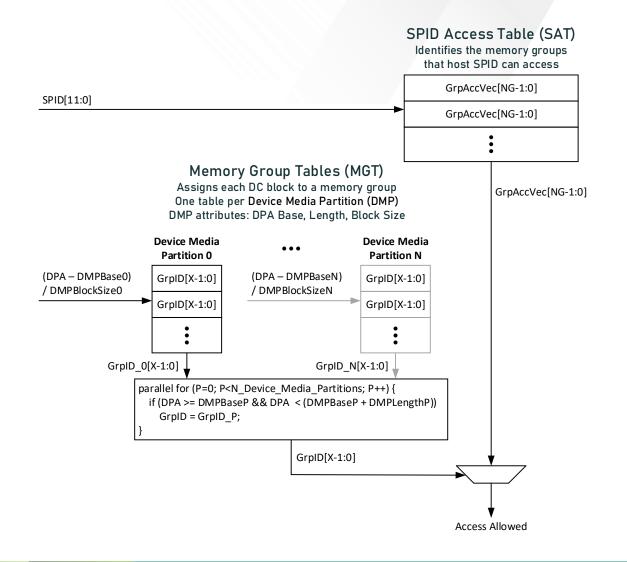

# CXL3 Fabric - GFD DC Access Protection

- GFD may have multiple DMPs with each DMP divided into fixed size blocks, and each block is assigned a memory group identifier

- SPID access table(SAT) identifies the memory groups a SPID (host) is allowed access

- The memory group table (MGT) identifies the memory group for each DMP block

- MGT and SAT structures are programmed by Fabric Manager

Compute

Express ∖Link™

- Storage and compute requirements continue to grow

- CXL3.0 enables a scalable rack scale memory fabric

- Starting the journey towards realizable memory centric computing

- Large opportunities lies ahead for standards-based rack scale compute and chiplet ecosystem (UCIE)

• Get Involved!

Copyright | CXL<sup>™</sup> Consortium 2022 - Hot Chips 2022 - CXL Tutorial